- #Modelsim altera post synthesis example 32 bit

- #Modelsim altera post synthesis example software

- #Modelsim altera post synthesis example code

function: tests the output of the codeword generator. I think that the problem may lie in my testbench but i don't know where. for instance symbols = 12, addr_width = 4, maxhight = 13 worked, but symbols = 50, addr_width = 6, maxhight = 51 don't. I change the amount of input by change the value of parameter TOTAL_SYMBOLS and parameter ADDR_WIDTH (size of address to account for total symbols = log2(TOTAL_SYMBOLS)) and maxhight (assume max hight of tree). Time: 0 ps Iteration: 0 Instance: /testbench/dut/gen/S1 File: C:/Users/PC/Desktop/huffman-coding-master/HuffmanEncodingVerilog-master/HuffmanEncodingVerilog-master/Vfiles/shfreg.v

#Modelsim altera post synthesis example software

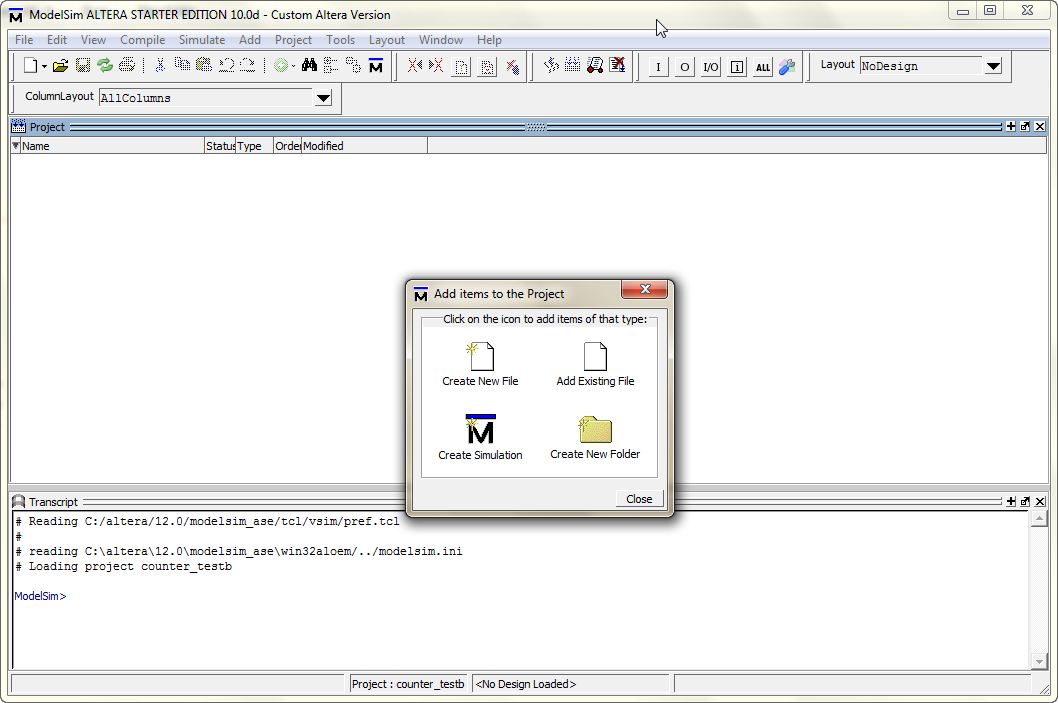

The software supports VHDL and Verilog HDL design entry, graphical-based design entry methods, and integrated system-level design tools. Please check your system for available memory and swap space. ModelSim ALTERA - Quartus II Software Quartus II software enables creation and delivery of FPGA, CPLD, and structured ASIC designs. Additionally, the Altera-provided functions may offer more efficient logic synthesis and device implementation. Using megafunc tions instead of coding your own logic saves valuable design time. The Device Under Test (DUT) in the example is a direct digital synthesis sine wave generator, as given below. provides parameterizable megafunctions that are optimized for Altera device architectures. Setting Up the EDA Simulator Execution Path To run an EDA simulator (e.g. An example follows, but there is no guarantee that my way of running ModelSim is even close to optimal. Performing Post-Synthesis Simulation You. ** Fatal: (vsim-4) ****** Memory allocation failure. Although ModelSim is integrated into Quartus (See doc by Julie Wang), I found it easier to use it stand-alone.

#Modelsim altera post synthesis example 32 bit

(i'm using the 32 bit version of modelsim altera, some suggest that i may run out of memory, but i'm pretty sure i'm far from reaching that)

but when i amp that number up, say 50 (which i have redeclare in the input file), i encounter an simulation error. Thing went smoothly for small number like 12 variable (12 numeric values of the amount of time that symbol appear aka frequencies). The result should display all the encoding binary of input then write it to the appointed hex file. On the Design menu, click Compile All to compile all the files and add them to the design library, for example, alteramfcomponents.vhd and alteramf.vhd.

#Modelsim altera post synthesis example code

I also recommend you warmly to explore Altera site where you will find a lot of code examples and tutorials. For example, compile the alteramf.vhd model files into the alteramf library, and compile the 220model.vhd model files into the lpm library. So i'm attempting a Huffman coding simulation from a list of symbol's character frequencies from hex file. I have several examples of code and testbenches at my site dedicated to FPGAs, which you can find visiting my profile.

0 kommentar(er)

0 kommentar(er)